相控陣雷達系統(tǒng)利用多個發(fā)射和接收通道來實現(xiàn)正常運行����。以前�����,這些平臺在構(gòu)造時都使用獨立的發(fā)射和接收集成電路(IC)。這些系統(tǒng)在發(fā)射(Tx)電路的數(shù)模轉(zhuǎn)換器(DAC)和接收(Rx)電路的模數(shù)轉(zhuǎn)換器(ADC)中分別使用單獨的芯片�����。這種區(qū)分使得許多系統(tǒng)尺寸龐大����、成本高昂且功耗高,如此才能獲得所需的通道數(shù)量��,進而發(fā)揮所需的功能���。由于制造和校準過程復(fù)雜�����,這些系統(tǒng)通常也需要很長時間才能上市���。但是,最近出現(xiàn)一種利用集成收發(fā)器的方法�����,它將許多曾經(jīng)被認為完全不同的功能融合到單個IC之中。這些IC助力實現(xiàn)了小尺寸���、低功耗和低成本�����、具有高通道數(shù)量的相控陣雷達系統(tǒng)���,且上市時間更短。

集成式收發(fā)器簡介

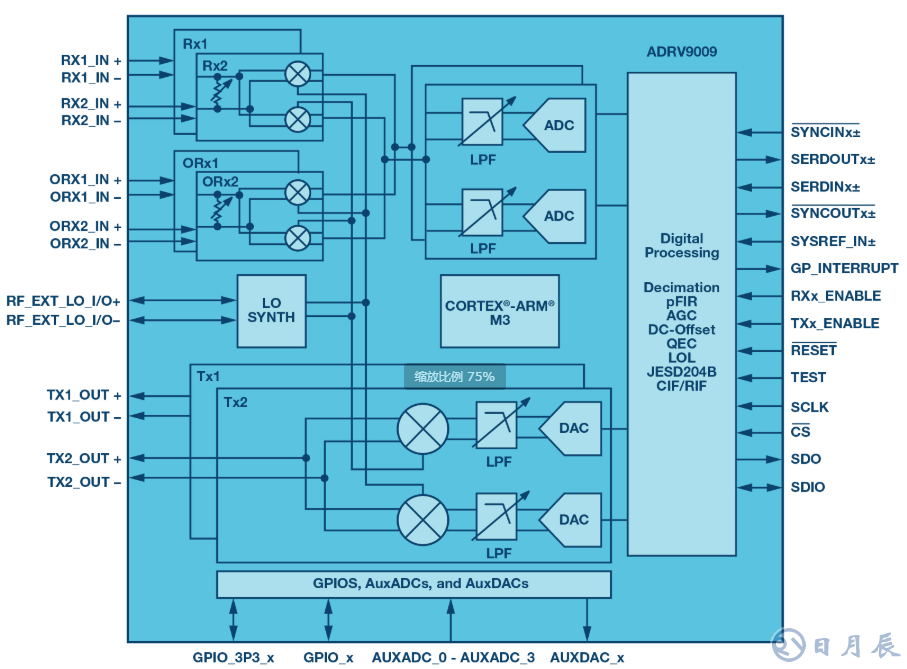

集成式收發(fā)器(例如圖1所示的收發(fā)器)將多種功能集成到單個IC上���。例如�����,新型收發(fā)器將DAC��、ADC��、本振(LO)頻率合成器����、微處理器���、混頻器����,以及更多功能集成到12 mm × 12 mm單芯片產(chǎn)品中���。此外�����,該產(chǎn)品還集成了兩個接收通道和兩個發(fā)射通道����,以及多個數(shù)字信號處理(DSP)組件�����,以獲得系統(tǒng)所需的瞬時帶寬��。還提供一個應(yīng)用程序接口(API)��,用于操作客戶平臺上的收發(fā)器���?����?梢岳闷瑑?nèi)前端網(wǎng)絡(luò)實現(xiàn)增益和衰減控制��。內(nèi)置的初始化和跟蹤校準例程用于提供許多通信和軍事應(yīng)用所需的性能����。

圖1.ADRV9009是將多種功能集成到單個IC中的集成式收發(fā)器示例。

這些集成式收發(fā)器能夠通過注入一個稱為REF_CLK的參考時鐘信號來創(chuàng)建發(fā)射器和接收器所需的所有時鐘信號���。然后����,由片內(nèi)鎖相環(huán)(PLL)合成DAC/ADC采樣��、LO生成和微處理器時鐘所需的所有時鐘�����。如果內(nèi)部LO相位噪聲不足以滿足客戶的應(yīng)用需求��,用戶可以選擇注入自己的低相位噪聲外部LO����。

來自部件的數(shù)據(jù)經(jīng)由標準化的JESD204b多千兆串行數(shù)據(jù)接口進行卸載����。這個接口支持同時接收和傳輸大量數(shù)據(jù)���。新集成式收發(fā)器解決方案可以幫助提供接口IP,幫助客戶加快上市時間����。如果需要確定性延遲和數(shù)據(jù)同步,用戶可以利用內(nèi)置的多芯片同步(MCS)特性����,并發(fā)出SYS_REF信號作為初始通道對齊序列(ILAS)的主時序基準。1

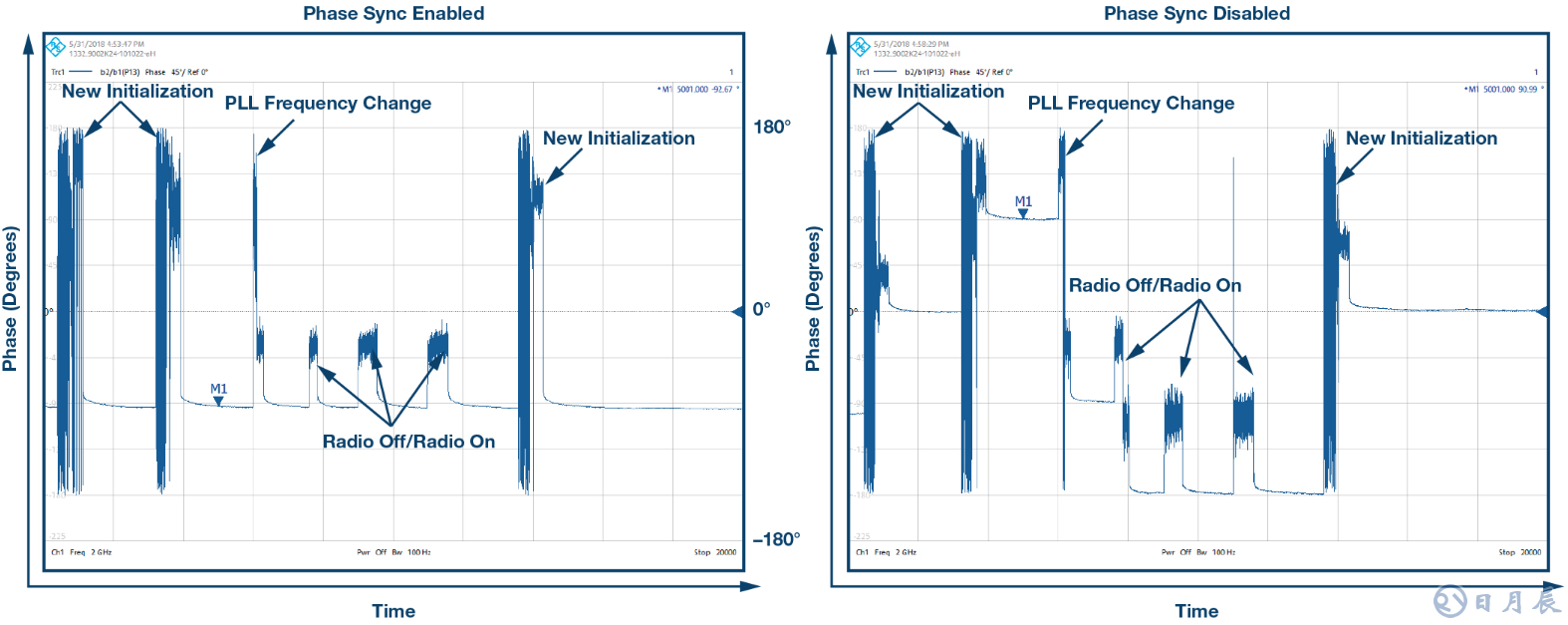

此外����,可以利用內(nèi)置的RFPLL相位同步特性,將發(fā)射或接收通道的LO相位設(shè)置為相對于主參考相位具備確定性��。通過利用MCS和RFPLL相位同步特性��,可以在初始化部件�����、頻率調(diào)諧,或者開關(guān)軟件上的無線電時復(fù)制相位對齊�����。圖2顯示了一個新型集成式收發(fā)器示例���,該收發(fā)器提供決定性相位�����,且支持所有這些特性�����。

圖2.內(nèi)置RFPLL相位同步特性讓系統(tǒng)與主參考源之間呈確定性相位關(guān)系����。

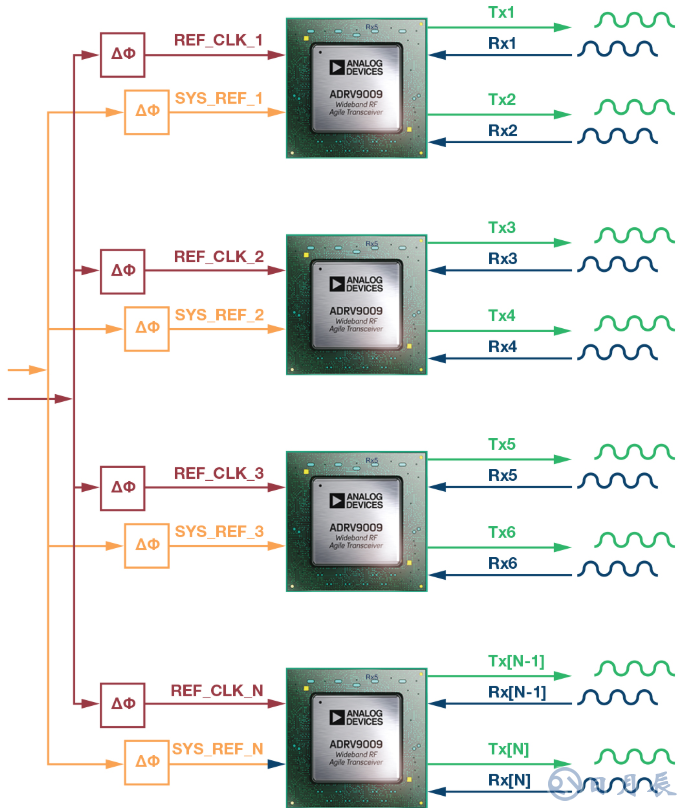

圖3.可使用多個集成式收發(fā)器來增加系統(tǒng)的通道數(shù)量�����。

使用多個集成式收發(fā)器

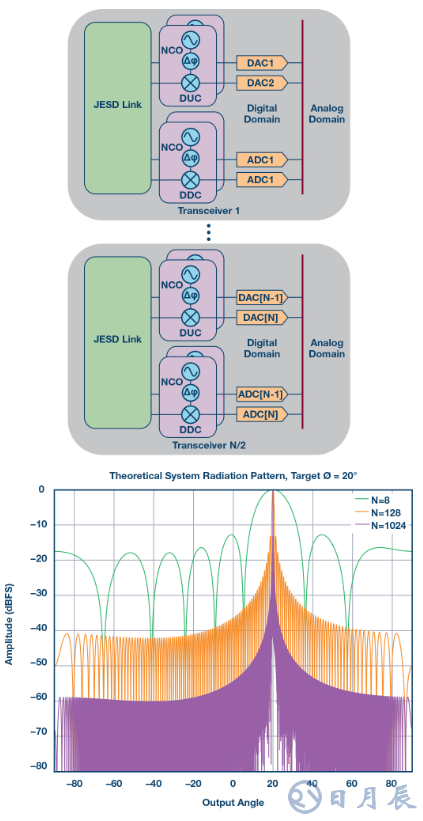

如果系統(tǒng)需要兩個以上接收器和兩個發(fā)射器���,用戶仍然能使用多個集成式收發(fā)器�����,從因為單芯片接收和發(fā)射通道實現(xiàn)的小尺寸中獲益�����。該技術(shù)的示例如圖3所示���。可以通過使用并發(fā)型SYS_REF脈沖來同時觸發(fā)所有IC的內(nèi)部分壓器���,從而同步多個集成式收發(fā)器����。這些SYS_REF脈沖可由時鐘芯片或基帶處理器發(fā)出���,附帶可編程延遲���,該延遲是造成各IC之間的路徑長度不匹配的原因?����?缍鄠€芯片的數(shù)據(jù)路徑和多個LO都可以是確定性的。

集成式收發(fā)器是支撐相控陣雷達平臺的中堅力量

通過使用同步集成式收發(fā)器來增加通道數(shù)量����,讓這些器件成為支撐相控陣雷達平臺的中堅力量。結(jié)合相位和幅度對齊的發(fā)射和接收通道時����,使用多個集成式收發(fā)器可以展示系統(tǒng)級的動態(tài)范圍、雜散和相位噪聲改善���。

片內(nèi)DSP特性���,例如數(shù)控振蕩器(NCO)和數(shù)字上變頻器,或者數(shù)字下變頻器(DDC)���,現(xiàn)在支持在單個IC內(nèi)采用系統(tǒng)級雜散去相關(guān)方法����。2

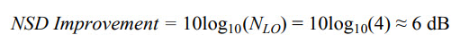

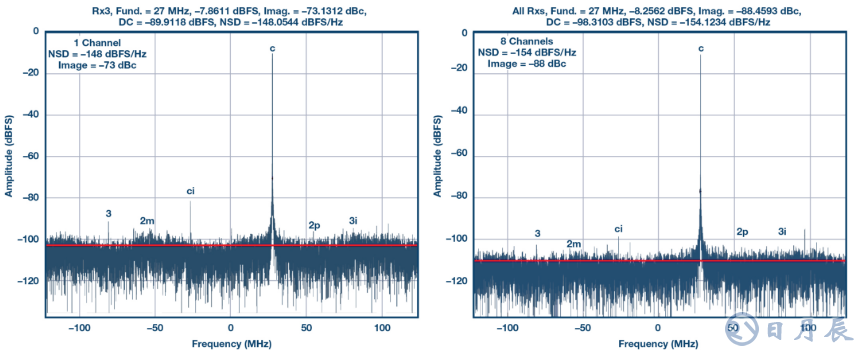

通過使用多個集成式收發(fā)器來組合收發(fā)器通道���,用于展示系統(tǒng)級噪聲譜密度(NSD)和雜散性能都得到改善�����。此舉通過降低系統(tǒng)的有效本底噪聲�����,同時維持通道的全部功能來改善相控陣雷達系統(tǒng)的動態(tài)范圍�����。圖4顯示了在集成多達8個集成式收發(fā)器接收通道��,有效增加相控陣系統(tǒng)中的位數(shù)之后�����,得出的系統(tǒng)級測量結(jié)果��。注意���,從一個通道增加到八個通道時,NSD和計算得出的本底噪聲(在各圖中用紅線表示)將增加6 dB�����。這是因為,雖然總共有8個通道���,但是在用于創(chuàng)建這8個通道的4個集成式收發(fā)器中���,只存在4個不同且不相關(guān)的LO(也就是說,NLO = 4)���。

因此實現(xiàn)了如下改善

得出的結(jié)果與集成式收發(fā)器提供的實驗性結(jié)果相近��。此外��,多余的成像頻率以不相關(guān)的方式聚合匯總����,實現(xiàn)系統(tǒng)級雜散性能改善����。隨著通道數(shù)量增加,性能會實現(xiàn)進一步改善����,從而實現(xiàn)可擴展的系統(tǒng)。

圖4.使用ADRV9009集成式收發(fā)器來集成接收通道可以降低噪聲譜密度����,并改善動態(tài)范圍�����。

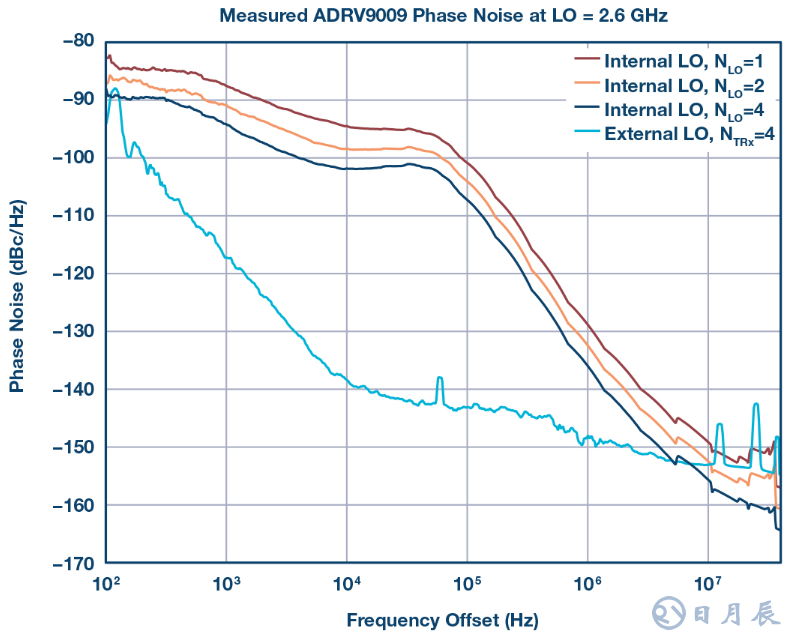

此外���,在對齊相位和集成多個集成式收發(fā)器通道之后,相控陣系統(tǒng)的相位噪聲可以得到改善����。從圖5最上方的三條曲線顯示的測量結(jié)果可以看出,在利用4個集成式收發(fā)器IC的內(nèi)部LO組合8個通道之后�����,相位噪聲性能得到了改善�����。再重復(fù)一遍���,存在4個不同且不相關(guān)的LO(也就是說,NLO = 4)時��,當(dāng)從1個發(fā)射通道增加為8個發(fā)射通道時,相位噪聲會增加6 dB����。增加通道數(shù)量可以進一步增加相控陣雷達系統(tǒng)的相位噪聲?��;蛘?���,可以將外部LO注入到由NTRx集成式收發(fā)器構(gòu)成的每個子陣列中�����,并從子陣列層級改善初始相位噪聲(如圖5中的藍色曲線所示)����。但是,如此一來����,該子陣列中的各元件因為都共用同一個LO源,就會互相關(guān)聯(lián)�����,所以無法自行在子陣列中提供通道聚合改善。對于圖5所示的外部LO相位噪聲數(shù)據(jù)���,其中使用了一個Rohde & Schwarz SMA100B信號發(fā)生器作為外部LO源����。

圖5.使用內(nèi)部LO時�����,集成多個ADRV9009的發(fā)射通道可以改善系統(tǒng)級相位噪聲性能��。

注入外部LO會改善子陣列的初始相位噪聲���。

圖6.DSP特性現(xiàn)在可以利用片內(nèi)NCO和DDC/DUC實現(xiàn)數(shù)字相移��。

增加通道數(shù)量����,優(yōu)化相移會使集成式收發(fā)器形成寬度變窄的波束����。

集成的DSP特性(例如NCO�����、數(shù)字移相器和DUC/DDC)允許在數(shù)字域內(nèi)實施基帶相移和頻率位移,進而允許在基于多通道��、集成式收發(fā)器的相控陣雷達系統(tǒng)中實施數(shù)字波束成型�����。將多個功能集成到單個IC上之后���,系統(tǒng)現(xiàn)在能夠在許多相關(guān)的相控陣應(yīng)用中�����,利用集成式收發(fā)器實現(xiàn)天線點陣間隔�����。利用更多收發(fā)器來增加通道數(shù)量一般可以讓波束變窄����,但會導(dǎo)致系統(tǒng)變大�����。但是,現(xiàn)在將多個功能集成到單個IC之后����,系統(tǒng)變大的比例還是要小于過去。使用MATLAB®模擬輻射圖之后�����,圖6顯示通道數(shù)量從N = 23增加到N = 210時��,波束如何變窄��,理論波瓣幅度如何變深�����。實際的功率零點將在天線設(shè)計中表明�����。

結(jié)論

在單個IC中集成多個數(shù)字和模擬功能可以實現(xiàn)更小型的相控陣雷達系統(tǒng)�����。這些系統(tǒng)支持實施數(shù)字波束成型和混合波束成型��,具體取決于系統(tǒng)規(guī)格�����。已經(jīng)證明使用ADI公司提供的ADRV9009可以實現(xiàn)系統(tǒng)級性能改善����。這些集成式器件讓許多新系統(tǒng)能夠使用相同的硬件來運行多個應(yīng)用。

參考資料

1 Harris����, J. 什么是JESD204標準,為什么我們要重視它��?ADI公司技術(shù)文章����,MS-2374,1-4��。2013年10月��。

2 Delos����, P.����、Jones��, M.����、Robertson, M. RF收發(fā)器支持在數(shù)字波束成型相控陣內(nèi)實施強制雜散去相關(guān)�����。ADI公司技術(shù)文章��。2018年8月�����。

作者簡介

Mike Jones是ADI公司航空航天和防務(wù)部的首席電氣設(shè)計工程師���,在美國北卡羅來納州格林斯博羅工作���。他于2016年加入ADI公司��。從2007年到2016年��,他在北卡羅來納州威爾明頓的通用電氣公司工作��,擔(dān)任微波光子學(xué)設(shè)計工程師,致力于研發(fā)核工業(yè)微波和光學(xué)解決方案��。他于2004年獲得北卡羅來納州立大學(xué)電氣工程學(xué)士學(xué)位和計算機工程學(xué)士學(xué)位���,2006年獲得北卡羅來納州立大學(xué)電氣工程碩士學(xué)位����。

Peter Delos是ADI公司航空航天和防務(wù)部的技術(shù)主管����,在美國北卡羅萊納州格林斯博羅工作。他于1990年獲得美國弗吉尼亞理工大學(xué)電氣工程學(xué)士學(xué)位����,并于2004年獲得美國新澤西理工學(xué)院電氣工程碩士學(xué)位。Peter擁有超過25年的行業(yè)經(jīng)驗���。其職業(yè)生涯的大部分時間花在高級RF/模擬系統(tǒng)的架構(gòu)��、PWB和IC設(shè)計上����。他目前專注于面向相控陣應(yīng)用的高性能接收器、波形發(fā)生器和頻率合成器設(shè)計的小型化工作���。

·上一篇: 三種調(diào)整處理器系統(tǒng)功耗的方法

·下一篇: 大氣壓平板等離子體反應(yīng)器及其技術(shù)難點是什么